Với xu hướng phát triển đó thì việc tích hợp càng nhiều linh kiện bán dẫn trong một đơn thể (IC) ngày càng được chú trọng, nhằm đáp ứng đà phát triển ngày càng cao của khoa học kỹ thuật , cũng như những ứng dụng thực tế.

Khi xuất xưởng, các IC thường được tích hợp sẳn với những chức năng riêng biệt, khi đó người sử dụng phải chọn lựa linh kiện sao cho việc thiết kế mạch hiệu quả nhất. Nhưng do độ tích hợp của IC cũng có giới hạn, và để linh hoạt hơn trong việc thực hiện những chức năng của người thiết kế, cũng như mối quan hệ mật thiết giữa nhà sản xuất và người sử dụng , cụ thể là tối ưu hóa khả năng ứng dụng của IC, nhà sản xuất đã cho ra một loại linh kiện đặc biệt mà chức năng của nó sẽ được người thiết kế quy định chứ không phải là nhà sản xuất nữa. Linh kiện đó được gọi chung là PLD ( Programmable Logic Device - Thiết bị logic lập trình được) .

Chúng ta sẽ khảo sát linh kiện PLD qua các IC cụ thể như PAL ( Programmable Array Logic devices ), GAL ( Generic array Logic devices ) .... Các IC PAL , GAL với độ tích hợp rất cao nên có thể thay thế hầu hết các loại IC TTL . Điều quan trọng và lý thú trong những IC này là chức năng của nó sẽ được người thiết kế quy định cho chính những ứng dụng của mình sao cho kinh tế , hiệu quả nhất .

Để thực hiện được việc thiết kế những ứng dụng trên IC PAL GAL... đòi hỏi người sử dụng cần phải kết hợp kiến thức cả về kỹ thuật số lẫn các ngôn ngữ lập trình cho thiết bị.

Cấu trúc linh kiện PLD

PLD ( Programmable Logic Device - Thiết bị logic lập trình được) thuộc họ bộ nhớ hàm ( Funtion Memory). PLD có dung lượng tương đối lớn , có kết cấu đơn giản nhất trong các linh kiện logic. Thông thường PLD cho phép người thiết kế tạo cho nó những chức năng riêng biệt ,bởi khi xuất xưởng nhà sản xuất chưa tạo cho nó một ứng dụng nào.

Cấu trúc mạch bên trong của một PLD thường là một chuỗi hình chữ nhật gồm những phần tử giống nhau (identical cell - ô nhớ đồng dạng). Hai mảng AND - OR có thể lập trình được nhờ tập hợp ngẫu nhiên các cổng logic và phần tử nhớ (OLMC - Output Logic Macro Cell ) .

PLD là mạch tích hợp của “SSI and MSI’ nên tính năng họat động của PLD linh hoạt , dễ sử dụng, dễ thiết kế và diện tích mạch giảm đáng kể so với việc thiết kế mạch bằng các IC rời chứa các cổng logic.

Khi dùng PLD việc thiết kế dễ dàng nhanh chóng nhờ nó có những phần mềm chuyên trách đảm nhiệm , làm cho công việc thiết kế logic đơn giản hơn. Ta cũng dễ dàng sửa lỗi chương trình, bổ sung, thay đổi cấu hình thiết kế bên trong để thực hiện một chức năng ứng dụng khác. Công nghệ linh kiện PLD sản xuất bằng EECMOS ( Electrically Erasable CMOS) tạo khả năng lập trình lại nhiều lần tốc độ cao, công suấât tiêu tán thấp, phương pháp lập trình đơn giản, giá thành thấp hơn mạch rời tương đương.

Giới thiệu về mảng lập trình

Như đã được giới thiệu ở trên, các loại linh kiện lập trình sử dụng 2 mảng AND, OR có thể lập trình được. Các ngõ vào và các đường tích (product terms - là số cổng AND) sẽ tạo nên một mảng cầu chì hiện diện đối với mỗi linh kiện, giao điểm giữa một đường tích và một đường ngõ vào cho ta xác định tọa độ của một cầu chì.

Để thực hiện một chức năng logic bằng các ngôn ngữ lập trình, trình biên dịch của ngôn ngữ đó sẽ rút gọn biểu thức sao cho tối ưu nhất, và thiết lập mảng cầu chì phù hợp với chức năng logic trên bằng cách hủy hoặc giữ một số cầu chì trong mảng cầu chì lập trình.

PLA (Programmable logic array):

PLA là linh kiện tổ hợp hai tầng (mảng) AND và OR có thể lập trình được để thực hiện bất cứ một biểu thức logic (tổng của các tích) nào . Một 'n.m' PLA với m ngõ vào, n ngõ ra và p biểu thức nhân thì có 2n ngõ vào cho mỗi cổng AND, m.p ngõ vào cho mỗi cổng OR .

Hình sau là mô hình của một PLA với 4 ngõ vào, 4 ngõ ra và 6 biểu thức nhân, mỗi ngõ vào được nối với một bộ đệm . Nó tạo ra hai đường tín hiệu ứng với hai mức logic khác nhau. Để thực hiện việc lập trình, các dấu nối bên trong được đánh dấu bởi dấu 'x' hay còn gọi là cầu chì nối, việc lập trình để thực hiện một chức năng logic bằng cách thành lập những mối cầu chì thực sự cần thiết. Số nối cầu chì trong một n.m PLA là 2.n.p cho chuỗi AND và m.p cho chuỗi OR.

PAL( Programmable Array Logic )

PAL là loại thiết bị đặc biệt của PLA, nó được sử dụng rộng rãi nhất trong các loại PLD hiện nay. Kết cấu bên trong tương đối đơn giản, chủ yếu lập trình bởi mảng AND, còn mảng OR cố định. Một ( n.m) PAL gồm p.m cổng AND với 2n ngõ vào, m cổng OR với p ngõ ra. Giá trị của p thay đổi tùy theo cấu trúc của mỗi loại PAL nhưng p thường nhỏ hơn nhiều so với 2n.

Một số loại PAL cấu trúc bên trong còn có bộ nhớ đầu ra (dạng Flip Flop), các mảng AND được lập trình để thực hiện chức năng logic của PAL. Đặc tính này không những thực hiện các chức năng bình thường mà còn làm tăng thêm đầu vào do các mảng OR trong bộ nhớ đầu ra, các chức năng của linh kiện logic loại này khi được ghi vào PAL thì không thể sửa chữa thay đổi. Trên thị trường còn có một loại PAL có thể sửa đổi chương trình (nạp lại nhiều lần) đó là PALCEXXXX (CE : CMOS Electrically Erasable ).

Chức năng của PAL : Thực hiện hầu hết các chứa năng logic tổ hợp và tuần tự như Multiplex, Decoder, Encoder, Counter, Shift Register...

GAL ( Generic Array Logic )

Có thể nói GAL bao gồm toàn bộ chức năng của PAL ( tương thích 100% ) nhưng khác với PAL là sau khi ghi các chức năng logic vào, nó có thể thay đổi và sửa lỗi được nhiều lần bằng phương pháp xóa bằng điện thường dùng. Điều dẫn đến việc sử dụng nó có phần thuận lợi hơn, có thể tiến hành bảo mật thông tin , do đó giá thành của GAL sẽ cao hơn các loại PAL thông thường. Tuy nhiên, ta có thể thay thế GAL bằng PALCE mà không ảnh hưởng gì về các chức năng logic.

Giải thích các ký hiệu cơ bản trên PAL , GAL

Ví dụ : PAL 20*8B# – 4XC PAL : Là họ IC lập trình được. 20 : Biểu thị cho số ngõ vào. * : H = High : Ngõ ra tác động mức thấp L = Low : Ngõ ra tác động mức cao. C = Complement : Ngõ ra tác động cả hai mức. R = Registed : Ngõ ra cấu trúc thanh ghi. X = Exclusive –OR : Ngõ ra dạng thanh ghi mà FF D được điều khiển bởi cổng logic X-OR thay vì cổng OR. V = Versatile : Ngõ ra cấu trúc dạng Macro cell. 8 : Biểu thị số ngõ ra. # : Biểu thị tốc độ truy xuất dữ liệu. Bỏ trống : Tốc độ chuẩn. A : Tốc độ cao. B : Tốc độ rất cao . C : Tốc độ cực cao. B : Công suất tiêu tán : Q : 1/4 công suất. H : 1/2 công suất. X : Loại vỏ linh kiện . C : Điều kiện hoạt động. C : thị trường (Commercial). I : công nghiệp.(Industrial).

Về cơ bản người ta chia PAL thành hai loại chuyên dùng ( phân biệt vào chữ số biểu thị trạng thái, cấu trúc ngõ ra ). * PAL dùng cho hệ tổ hợp gồm PAL loại H,C,L. * PAL dùng cho hệ tuần tự gồm PAL loại R,X.

Riêng PAL loại V là loại linh hoạt có thể dùng cho cả hai loại tổ hợp và tuần tự tùy theo người thiết kế khai báo trong chương trình lập trình. GAL ký hiệu cũng tương tự như PAL ở trên. Các ký hiệu sẽ được nói rõ hơn khi đi sâu vào từng loại một. Các phần sau sẽ đi vào chi tiết các linh kiện PAL, GAL hiện có trên thị trường.

Phần này chúng ta sẽ đi vào chi tiết các linh kiện PAL CE16V8 hiện có trên thị trường.

PAL CE16V8

Linh kiện có trên thị trường: PAL CE 16V8H-5PCX

+ PAL (Programmable Arr ay Logic ) : mảng logic có thể lập trình được . + CE (CMOS Electrically Erasable ) : công nghệ CMOS có thể xóa. + 16 (Input) : số mảng (array) ở ngõ vào. + V (Versatile ) : loại ngõ ra linh hoạt . + 8 (Output) : số FLIP-FLOP ở ngõ ra. + H : Công suất tiêu tán . H : ½ công suất . Q : ¼ công suất . + -5 : thời gian truyền . -5 = 5 ns -7 = 7.5 ns -10 = 10 ns -15 = 15 ns -20 = 20 ns -25 = 25 ns + P : kiểu vỏ linh kiện ( Plastic DIP - PD 020) + C : Điều kiện hoạt động . C : Linh kiện ngoài thị trường 00C -> 75oC I : Linh kiện dùng trong công nghiệp -40oC -> 850C + X : Tốc độ truy xuất ; B (Blanking - để trống) : tốc độ chuẩn .

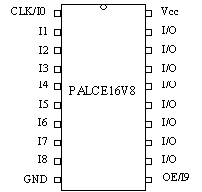

PALCE16V8 là linh kiện tiên tiến nhất trong họ IC PAL. Đây là một vi mạch lập trình có khả năng ứng dụng cao, chúng được sản xuất bằng công nghệ EECMOS, tốc độ chuyển trạng thái nhanh, công suất tiêu tán thấp, lập trình dễ dàng, gia tăng độ tin cậy, lưu trữ dữ liệu được lâu, có thể ghi xóa được nhiều lần . PALCE 16V8 gồm 20 chân có sơ đồ khối biểu diễn như hình trên.

Cấu trúc sơ đồ khối của PALCE 16V8 trên có thể coi như sơ đồ khối của họ PAL16XX.... và hầu hết họ PLD tổ hợp 20 chân. PAL16V8 gồm một ma trận AND có khả năng lập trình với kích thước 32x64 , 8 khối logic đầu ra OLMC ( Out Put Logic Macrocell ) độc lập nhau MC0 -> MC7 . Sơ đồ khối logic đầu ra được minh họa ở hình 7 cho thấy chi tiết một MACROCELL xuất của các loại PALCE . Ngõ ra được điều khiển bằng cách lập trình cho MACROCELL này, trong đó chân 1 và chân 11 được coi là chân cho dữ liệu vào mảng lập trình hoặc là CLK và OE (Output Enable ) đối với tất cả các OLMC .

Khối logic đầu ra có thể làm việc trong các cấu hình kiểu ngõ ra thanh ghi , ngõ ra tổ hợp, ngõ ra tổ hợp I/O hay là ngõ vào. Trong khối OLMC, mỗi cổng OR lái một tế bào vĩ mô xuất (output macrocell). Các tín hiệu cho phép xuất là OE hay một biểu thức nhân là 1 trong 8 đường nối đến cổng OR. Khi OLMC thực hiện chức năng cho dữ liệu vào thì chân OE ,CLK xem như được thay thế cho đường hồi tiếp của hai khối MC0, MC7 (không có đường hồi tiếp ).

MACROCELL điều khiển cấu hình bằng các tín hiệu : SR1, SLOx, SGO, SG1, CLK. Cấu hình mode ứng với giá trị các tín hiệu như sau : + Cấu trúc kiểu thanh ghi : Trong kiểu này giá trị các tín hiệu điều khiển được đặt như sau : SG0 = 0 , SG1 = 1 SL0x = 0 8 biểu thức nhân được nối toàn bộ vào cổng OR . Đường hồi tiếp vào mảng lập trình lấy từ ngõ /Q của FF ,tín hiệu cho phép xuất là OE. + Cấu trúc kiểu tổ hợp : Ngõ ra không phải là thanh ghi . Ở đây các tín hiệu điều khiển được đặt là : SG0 = 1 , SG1 = 0 , SLOx = 0 Tổ hợp I/O không phải là thanh ghi. Ở đây các tín hiệu điều khiển được đặt : SG0 = 1 , SG1 = 1 , SLOx = 1 Tổ hợp I/O là thanh ghi . Các tín hiệu điều khiển được đặt như sau : SG0 = 0 , SG1 = 1 , SLOx = 1 + Cấu trúc kiểu ngõ vào . Các tín hiệu điều khiển được đặt như sau : SG0 = 1 , SG1 = 0 , SLOx = 1

Sơ đồ chân

Sơ đồ của OPMC(Output Macro Cell)

Các mode hoạt động của PALCE 16V8

PALCE 16V8 hoạt động theo 3 mode sau đây + Mode đơn (Simple Mode ): Trong mode đơn 8 khối nhân được nối với khối tổng. Chân 15, 16 luôn luôn được định là ngõ ra tổ hợp. Các MACROCELL khác có thể là ngõ vào hay ra tổ hợp với sự hồi tiếp từ ngõ ra về chuỗi cổng AND. Chân 1, 11 là ngõ vào thông thường, mode này được chọn khi các ngõ ra đều là tổ hợp, không có tín hiệu điều khiển OE.

+ Mode phức (Complex Mode ): Trong mode phức những chức năng ngõ ra tổ hợp và ngõ vào/ra hai chiều (I/O) được sử dụng, chân 1, 2,...11 là ngõ vào chuỗi, chân 13,14,... 18 là ngõ ra có đường hồi tiếp về chuỗi cổng AND, chân 12,19 chỉ là ngõ ra không được dùng làm ngõ vào. 7 khối nhân nối đến khối tổng, khối nhân còn lại dùng tạo tín hiệu cho phép xuất (OE : Output Enable). Mode này sẽ được chọn khi ngõ ra tổ hợp có tín hiệu điều khiển OE.

+ Mode thanh ghi (Registetd Mode): Mode này sẽ được dùng khi ngõ của một chức năng thiết kế cần một hay nhiều thanh ghi ( tối đa 8 thanh ghi tương ứng với 8 FF-D) . Mỗi Macrocell có thể được định chức năng như một ngõ ra tổ hợp, một ngõ vào ra hai chiều (I/O) hay một ngõ vào. Trường hợp Macrocell là ngõ ra thanh ghi được phép xuất bởi chân OE, thanh ghi được kích bởi tín hiệu xung Ck từ ngõ vào CLK. 8 khối nhân (hay làđường tích - product term) được nối với 1 khối tổng. Trường hợp Macrocell được định chức năng ngõ ra là tổ hợp thì tín hiệu cho phép xuất được lấy từ một khối nhân, bảy khối nhân còn lại sẽ được nối với một khối tổng.

GAL là linh kiện được xếp vào thế hệ thứ hai sau PAL do đó nó là linh kiện được cải tiến rất nhiều so với PAL, chế tạo từ công nghệ CMOS, tốc độ xử lý nhanh, xóa chương trình bằng xung điện một cách nhanh chóng (<100ms>

GAL 16V8

GAL16V8 thực hiện các chức năng logic bằng cách lập trình trên các OLMC. Có ba mode hoạt động : SIMPLE, COMPLEX , REGISTED, được điều khiển bởi các bit như sau :

Bit SYN , ACO : điều khiển mode cho tất cả các MACROCELL . Bit XOR của mỗi MACROCELL: điều khiển giá trị xuất của MACROCELL. Bit AC1 : điều khiển cấu hình ngõ ra của MACROCELL .

Chi tiết của các mode sẽ được mô tả sau đây :

+ Registred mode ( mode thanh ghi ): Trong mode này cấu hình của mỗi MACROCELL (MRC) được xem như ngõ ra thanh ghi hoặc ngõ vào/ra I/O , vậy ta có đến 8 thanh ghi hoặc 8 ngõ vào ra I/O tương ứng với các MRC trong linh kiện. Mỗi ngõ ra I/O có 8 biểu thức nhân (hay là đường tích - product term) . Tất cả các MRC này được nối chung với tín hiệu CLOCK (chân số 1) ,tín hiệu OUTPUT ENABLE (chân số 11) , các bit định vị mode này có giá trị như hình sau.

+ Complex mode (mode phức ): Ở mode này cấu hình của MRC được tạo như ngõ ra hoặc ngõ vào/ra I/O. Trong mode này thì chỉ có sáu ngõ vào ra I/O , 2 MRC còn lại chỉ thực hiện chức năng của ngõ ra ( chân số 12 , 19), không có ngõ hồi tiếp như các MRC khác . Nếu yêu cầu thiết kế cần dùng đến 8 ngõ ra I/O ta nên nghĩ đến việc dùng mode thanh ghi . Có 7 biểu thức nhân được nối đến ngõ ra của một MRC, biểu thức nhân còn lại được dùng vào việc lập trình cho phép xuất giá trị ngõ ra. Chân 1, 11 đóng vai trò là chân đưa dữ liệu vào mảng lập trình AND.

+ Simple mode (mode đơn ): Cấu hình của mode này được xem như ngõ vào hoặc ngõ ra tổ hợp .Tất cả các ngõ ra có tới 8 biểu thức nhân được nối đến, hai MRC (chân 15,16) đơn thuần chỉ là ngõ ra không có đường hồi tiếp . Chân 1, 11 luôn là ngõ cho tín hiệu vào mảng AND .

Mode đơn của GAL16V8

Mode phức của GAL16V8

Mode thanh ghi của GAL16V8

Giống như ROM hay PROM, một PLD có thể được lập trình cơ bản bằng cách truy xuất trực tiếp đến khối cầu chì, hay diode . Tuy nhiên rất ít người thiết kế làm việc đó, ngay cả việc gián tiếp qua một file văn bản thập lục. Thay vào đó người thiết kế dùng một số ngôn ngữ lập trình cho PLD đề định ra những chức năng logic cần thiết cho những ứng dụng.

Giống như ROM hay PROM, một PLD có thể được lập trình cơ bản bằng cách truy xuất trực tiếp đến khối cầu chì, hay diode . Tuy nhiên rất ít người thiết kế làm việc đó, ngay cả việc gián tiếp qua một file văn bản thập lục. Thay vào đó người thiết kế dùng một số ngôn ngữ lập trình cho PLD đề định ra những chức năng logic cần thiết cho những ứng dụng.

Một ngôn ngữ lập trình được trợ giúp bởi một bộ xử lý ngôn ngữ (Language Prosessor) hay gọi đơn giản là bộ biên dịch . Bộ biên dịch này có chức năng chuyển một chương trình nguồn (ở dạng văn bản) được viết bằng ngôn ngữ lập trình sang một tập tin sơ đồ cầu chì (tập tin dạng *.jed) theo chuẩn JEDEC (Joint Electron Device Egineering Council). Sau đó, tập tin *.jed sẽ được nạp cho linh kiện PLD thông qua một thiết bị nạp đặt biệt. Mặc dù hầu hết PLD có thể lập trình thật sự với những biểu thức tổng tích, nhưng với ngôn ngữ lập trình cho PLD cho phép viết các biểu thức dưới bất cứ dạng nào, bộ biên dịch sẽ tính toán và rút gọn biểu thức cho phù hợp nếu có thể với một cấu trúc PLD cho trước .

Những bộ biên dịch tiến bộ còn cho phép định nghĩa lưu đồ trạng thái (state machine) đối với PLD tuần tự, tự động chọn PLD thích hợp, trình bày sự thực hiện gán trạng thái và phát triển những công thức logic.

Sau đây là 3 ngôn ngữ lập trình phổ biến sẽ được đề cập ở phần sau: + ABEL(Advanced Boolean Expression Language) : chạy trên nền DOS. + WINCUPL(Windows Universal Compiler for Programmable Logic) : chạy trên nền WINDOWS. + PALASM (PAL Assembler and Simulator): chạy trên nền DOS.

Ngôn ngữ lập trình ABEL(Advanced Boolean Equation Language)

Cấu trúc cú pháp Các phát biểu * Phát biểu module : CÚ PHÁP : Module [(Dummy-arg[...])] Module: Là tên hợp lệ được đặt làm tên gọi cho một module chương trình. Một chương trình lớn có thể có nhiều module, mỗi module có tựa (title ) , các khai báo (declaration ) ,các biểu thức (equation ) riêng Tên phải bắt đầu với một chữ cái hay dấu gạch dưới ‘_’ dài tối đa 31 chữ cái chữ số hay dấu gạch dưới : VÍ DỤ : Module Counter 16;

* Phát biểu Title : CÚ PHÁP : Title “string” Chỉ ra một chuỗi tựa (title string ) sẽ được chèn vào các file dữ liệu (các tập tin *.doc, *.jed …). Chuỗi là một dãy kí tự được đóng trong hai dấu nháy đơn (' ') . VÍ DỤ : TITLE ‘couter module_16 using PAL16V8’

* Phát biểu Equation : CÚ PHÁP : Equations Để chỉ ra những biểu thức logic theo sau định nghĩa tín hiệu ra (output signal) như là các hàm của tín hiệu vào . Biểu thức logic viết dưới dạng các phát biểu gán bằng ngôn ngữ lập trình, mỗi biếu thức được kết thúc bằng một dấu chấm phẩy(;) . VÍ DỤ : Equations Q0 = D1 & D2 ; Q1 = D1 # D2 ;

* Phát biểu Truth_table: CÚ PHÁP : Truth_table ( input -> output ) Hay Truth_table ( input :> reg_outs ) Hay Truth table ( input:>reg_out -> outputs) Input ,Output : Là các ngõ vào ngõ ra của hàm logic . Reg_outs : Các ngõ ra của hàm thanh ghi (FF). Dấu -> : Biểu diễn hệ tổ hợp . Dấu :> : Biểu diễn hệ tuần tự . Truth_ table ghi lại đáp ứng của các tín hiệu ngõ ra theo các tín hiệu ngõ vào. Truth_table có thể thay thế hoặc bổ sung thêm cho các biểu thức ( Equation), hay sơ đồ trạng thái (State Diagram). VÍ DỤ : Truth _table ([A,B -> C ]) [0,1] -> 1 ; [1,0] -> 1 ; [1,1] -> 1 ; [0,0 ] -> 0 ; Bảng sự thật trên biểu diễn cho biểu thức C = A + B .

* Phát biểu state_diagram :

CÚ PHÁP : State_diagram

Phát biểu State _diagram định nghĩa các biến trạng thái tham gia hoạt động trong lưu đồ trạng thái.

VÍ DỤ : giả sử ta có hai ngõ vào X0 và X1 ngõ ra là Z. Đồ hình trạng thái có ba trạng thái kí hiệu S0, S1, S2 có hai biến trạng thái [Q1 ,Q0 ] = Q (hai ngõ ra của FF). Đoạn chương trình sau tương ứng với lưu đồ trạng thái trên : State_diagram Q State S0: if (X1& X0 == 0) then S2 else S1 ; State S1: Z=1; goto S2 ; State S2: Z=0 ; goto S0 ;

* Phát biểu Goto : CÚ PHÁP : Goto state exp . Nhảy đến trạng thái kế tiếp không có ràng buộc điều kiện . VÍ DỤ : Si : goto Sj ; Từ trạng thái Si nhảy đến trạng thái Sj ; Si : goto X+Y -//- X+Y ;

* Phát biểu If-then-else : CÚ PHÁP : if exps then stateexp1 [ese state exp2] ; hay if exps1 then stateexps1 else if exps2 then stateexps2 ................. [ else if .... ] else state exp n; Exps : Là bất cứ biểu thức nào hợp lệ . State exp1 ;state exp2.....: Biểu thức biểu diễn trạng thái kế tiếp.

Phát biểu IF-THEN-ELSE : Mô tả sự chuyên trạng thái theo điều kiện ngõ vào. Nếu biểu thức sau từ khóa IF là đúng thì chuyển hướng đến trạng thái ngay sau từ khóa THEN, nếu sai thì chuyển đến trạng thái ngay sau từ khóa ELSE. Các phát biểu có thể được nối tiếp nhau liên tiếp nhưng kết thúc phải có dấu chấm phẩy (;).

VÍ DỤ : State 1:if (A==B) then 2. Nếu A=B chuyển đến trạng thái 2 State 2:if A then 3 else 4 . Nếu A đúng chuyển đến trạng thái 3 Nếu A sai chuyển đến trang thái 4.

* Phát biểu Case : CÚ PHÁP : Case [exps1: state exps1 ;] [expsXi :state expsXi ;] End case; Phát biểu CASE mô tả sự chuyển biến trạng thái trong trường hợp có nhiều điều kiện tác động đến chương trình .

VÍ DỤ : State 0 : case A == 0 :1 ; A == 1 :2 ; A == 2 :3 ; A == 3 :0 ; end case ;

* Phát biểu Test_vectors : CÚ PHÁP : test_vectors[‘note’](input -> output) [invalues -> outvalues ] Note là một chuỗi ký tự để mô tả các test_vectors . Input là một ký hiệu hay tập hợp các ký hiệu của các tín hiệu ngõ vào hay hồi tiếp về ngõ vào của hệ. Output : Ký hiệu các tín hiệu ngõ ra . Invalues : Các giá trị gán bởi ngõ vào . Out : Là giá trị ngõ ra, hàm logic của các tín hiệu ngõ vào, hay giá trị trạng thái của hệ tuần tự.

CÁCH DÙNG : Dùng cú pháp Test_vectors để mô phỏng hoạt động của hệ. Kiểm tra các chức năng của hệ khi chạy chương trình mô phỏng.

VÍ DỤ: Equation C = A & B ; “C = A. B D = A # B ; “D = A+B Test_vestor ([ A , B] -> [ C , D ]) [ 0 , 0] -> [ 0 , 0 ]; [ 0 , 1] -> [ 0 , 1 ]; [ 1 , 0] -> [ 0 , 1 ]; [ 1 , 1] -> [ 1 , 1 ];

* Phát biểu Istype : CÚ PHÁP : signal [,signal]....istype ‘ attr [,attr ]...’; Hay signal [,signal]...pinistype ‘ attr [,attr ]...’; Signal : Ký hiệu của pin, node . Attr : Là một chuỗi ký tự xác định các thuộc tính (attribution) chứa các signal.

MụC ĐÍCH - CÁCH DÙNG : Phát biểu Istype định nghĩa lại các thuộc tính của chân, nút của linh kiện. Các thuộc tính của pin hay node có thể khai báo trên một dòng. Các thuộc tính hợp lệ là : ‘Buffer‘ : Đệm . ‘Com’ : Hệ tổ hợp. ‘Invert’ : Đảo . ‘Neg’ : Tích cực mức cao. ‘Reg’ : Thanh ghi hệ tuần tự . ‘Reg-D ,Reg-T........các loại thanh ghi.

VÍ DỤ : FO, A là tín hiệu ra của thanh ghi tác động mức thấp, được khai báo như sau: Output pin 15 istype ‘reg,invert’;

* Phát biểu End:

CÚ PHÁP : End

hay End

* Các khai báo khác : + Chân - pin : CÚ PHÁP : [!]pin_id[,[!]pin_id...]pin[#[,pin#]]istype’attr’; Pin_id : Ký hiệu dùng để đặt tên cho chân của linh kiện. Pin# : Số thứ tự chân trên linh kiêïn thiết kế . Attr : Là chuỗi ký tự xác định thuộc tính chân . [!] : Ký hiệu NOT ,tác động ở mức thấp. Từ khóa pin dùng để khai báo những tín hiệu Input , Output ,In/Out đã được quy định sẵn trên linh kiện. Khai báo còn có thể định nghĩa thuộc tính chân .

VÍ DỤ : !Q0 ,RESET, S1 pin 12,13,5 ; Có nghĩa là ta gán Q0 vào chân 12, Q0 tác động ở mức thấp. RESET ... 13 ........ cao. S1 ... 5 ........ cao.

+ Nút - node : CÚ PHÁP : [!]node_id[,[!]node_id...]node[node#[,node#....][istype,attr’]]; Node_id : Ký hiệu dùng để đặt tên cho một nút. Node# : Số thứ tự của nút trên linh liện, số nút do nhà sản xuất quy định. Từ khóa NODE dùng để khai báo những tín hiệu gán cho nút.

VÍ DỤ : C node istype ‘reg’; A,B NODE 25,26 ; Xác định C là một nút trong linh kiện, thuộc tính thanh ghi . Gán tên A cho nút 25 và tên B cho nút 26.

+ Linh kiện - device : CÚ PHÁP : Device_id device real device ; Device_id : Tên của file fusemap (dạng * .jed). Real device : Mô tả mã số linh kiện (PLD) đặt giữa hai dấu (‘). Khai báo linh kiện để gắn tên linh kiện sử dụng trong một module với một linh kiện thật . Phải có dấu (;) sau khai báo .

VÍ DỤ : D1 device ‘PAL 16L8’; Khai báo trên cho biết D1 là PAL16 L8, và chương trình ABEL sẽ tạo ra tập tin sơ đồ cầu chì có tên là D1.jed .

+ Hằng - constant : CÚ PHÁP : id[,id] ..... = exp [ , exp ]...; Id : Ký hiệu đặt tên cho hằng. Exp : Xác định giá trị hằng Khai báo hằng dùng để định nghĩa hằng số đươc dùng trong một module . VÍ DỤ : X = X ; ‘X mang ý nghĩa không xác định’. Z = Z ; ‘Z mang ý nghĩa tổng trở cao’ C = C ; ‘C mang ý nghĩa tác động cạnh lên’. A = ^b01; ‘A được gán bởi giá trị là số nhị phân’ B = ^h16; ‘H được gán bởi giá trị là số hex’ C = 157 ; ‘C được gán bởi giá trị là số thập phân'

+ Tập hợp - set : ĐịNH NGHĨA : Tập hợp các tín hiệu và hằng số mà thao tác thực hiện như là một đơn vị. Bất cứ một thao tác nào áp dụng cho một tập hợp sẽ được áp dụng cho mỗi phần tử trong tập hợp . Tập hợp sẽ làm đơn giản việc mô tả logic và các vector thử bằng cách chỉ dùng tên gọi tập hợp . Một tập hợp được biểu diễn bởi một danh sách các hằng số và tín hiệu, các hằng số và tín hiệu này được ngăn cách bởi dấu chấm phẩy (;) hay dấu (...) , được đặt trong dấu ngoặc ([ ]) sau mỗi khai báo phải có dấu (;).

VÍ DỤ : Mulout = [ B0,B1,B2,B3,B4,B5,B6,B7 ]; Mulout = [ B0...B7 ]; Khai báo trên là gán Mulout là tên một tập hợp gồm 8 tín hiệu từ B0...B7 .

+ Macro : CÚ PHÁP : Macro_id macro[(dummy_arg[,dummy_arg]...)]{block}; Macro_id : Một ký hiệu đạêt tên cho macro . Dummy_arg : Thông số hình thức . Block : Là các biểu thức logic . Khai báo Macro để định nghĩa một macro thực hiện chức năng các phép toán, chỉ định nghĩa Macro một lần ở phần khai báo macro trong module và sẽ được dùng bất cứ nơi nào khác trong module . Macro chỉ được dùng trong module nào mà nó được khai báo .

VÍ DỤ : NAND 3 macro (A,B,C) {!(A&B&C)} NAND 3 : là macro thực hiện chức năng hàm logic đảo của A.B.C với A, B, C là các thông số hình thức . Trong module ta khai báo macro như sau : D = NAND 3 (clock, hello, hi ) ; Khi đó kết quả là : D = !(CLOCK&HELLO&HI );

+ Enable : CÚ PHÁP : Enable output_id = [!]expr ; Output_id : Ký hiệu được đặt tên cho mỗi ngõ ra hay tổ hợp các ngõ ra. Expr : Biểu thức logic . - Khai báo ENABLE cho phép ngõ ra ba trạng thái hoạt động theo tín hiệu điều khiển bởi giá trị của Exprt . - Sử dụng khai báo này sau khai báo của biểu thức .

VÍ DỤ : OE pin 11; F0,F1,F2,F3 pin 19,18,17,16 ; COUNT = [ F0,F1,F2,F3 ] ; Equation Enable COUNT = ! OE ; Các ngõ ra từ F0.......F3 trong tập hợp COUNT là ngõ ra ba trang thái được truy xuất khi OE = 0 và cấm khi OE = 1 (ở trạng thái tổng trở cao ). Có thể thay thế tiếp vị ngữ OE thay cho ENABLE .

* Các toán tử ( Operator ) : - Toán tử chuẩn (standard) : ! : NOT ; # : OR ; & : AND ; $ : XOR ; !$ : XNOR ; = : Toán tử gán cho biểu thức tổ hợp . := : Toán tử gán cho biểu thức thanh ghi (tuần tự ). Ngoài ra từ khóa @ALTERNATE thông báo cho trình biên dịch biết chương trình đang sử dụng bộ toán tử tương đương (ALTERNATE), thay thế cho bộ toán tử chuẩn . Các toán tử thay thế được biểu diễn như sau :

/ : NOT ; * : AND ; + : OR ; :+: : XOR ; :*: : XNOR ;

Muốn sử dụng bộ toán tử thay thế cần phải có từ khóa @ALTERNATE ở đầu module chương trình, khi đó trình biên dịch mới hiểu các toán tử thay thế .

- Các toán tử so sánh (comparator): = = : bằng ; ! = : không bằng ; < : nhỏ hơn ; > : lớn hơn ; <= : nhỏ hơn hoăc bằng ; >= : lớn hơn hoăc bằng ; Ta có thể viết các biểu thức điều kiện kết hợp với các toán tử trên, các biểu thức sẽ có giá trị 1 nếu biểu thức đúng (thỏa điều kiện ) ,có giá trị 0 nếu không thỏa điều kiện .

VÍ DỤ : Q = ( P = = 1 ) ; Khi đó Q = 1 nếu P = 1. Q = 0 nếu P != 1 .

* Các tiếp đầu ngữ, tiếp vị ngữ : + Tiếp đầu ngữ (prefix) : Toán tử NOT (! Hay / ) được dùng như tiếp đầu ngữ để báo cho trình biên dịch biết tín hiệu đang hoạt động ở mức tác động là HIGH hay LOW (1 hay 0) .

VÍ DỤ : !Q0 pin 15 ; Tương đương với Q0 pin 15 is type ‘neg’ ; Q0 tác động ở mức thấp ;

+ Tiếp vị ngữ (suffix ) : Tiếp vị ngữ thường dùng trong chế đỘ thanh ghi , để truy xuất các chế độ liên quan đến thanh ghi . VÍ DỤ : Q0.CK truy xuất đến chân CLK đối với tín hiệu ra Q0 ở chế độ thanh ghi . Sử dụng tương tự đối với các tiếp vị ngữ sau : .RE, .PR, .D, .T .... .RE : có sử dụng chân reset của FlipFlop. .PR : có sử dụng chân preset của FlipFlop. .D : chân của FlipFlop D . .T : chân của FlipFlop T . Tiếp vị ngữ . OE cho phép truy xuất đến ngõ ra 3 trạng thái . Out .OE = ! ENABLE ; ENABLE = 0 ngõ ra được phép xuất . ENABLE = 1 ngõ ra không được phép xuất .

* Ghi chú (comment ) : Các ghi chú, minh họa, giải thích chương trình thường bắt đầu bằng dấu (“) phía bên trái hoặc xuống dòng . VÍ DỤ : Q1,Q2,Q3 pin 15,16,17 “chân output

* Kết cấu cơ bản một chương trình ABEL: Module Module_name Title String Device_indentifier Device device_type @alternate " có hoặc không cũng được Pin declarations “comment Other declarations Equations End module_name

Cấu trúc cú pháp

+ APPEND : Từ khóa này cho phép gán các biến bằng tổ hợp các biểu thức với toán tử OR, các biểu thức này là những từ khóa APPEND riêng lẻ . CÚ PHÁP : APPEND :[ ! ]var [. ext ] = expr ; ! : là toán tử lấy giá trị đảo của biến . var : tên của một biến . .ext : phần cho phép mở rộng chức năng của biến . = : toán tử gán . expr : các biều thức hợp lệ . ; : dấu kết thúc câu lệnh . VÍ DỤ : APPEND Y = A0 & A1 ; APPEND Y = B0 & B1 ; APPEND Y = C0 & C1 ; Khi ta dùng biến Y sau ba từ khóa trên thì nó sẽ được gán một giá trị tương đương với biểu thức sau : Y = ( A0 & A1 ) # ( B0 & B1 ) # ( C0 & C1 ) ;

+ CONDITION : Từ khóa này được khai báo khi chuyển biến trạng thái với điều kiện ngõ ra đồng bộ. Các biến logic sẽ được đặt trong mọi biểu thức chuyển trạng thái .

CÚ PHÁP : CONDITION { IF : expr0 OUT var ; … … … IF : exprN OUT var ;

GIẢI THÍCH: { : Bắt đầu những dòng lệnh điều kiện . expr : Những biểu thức hợp lệ . var : Là tên biến ra được khai báo ở trên . ; : Dấu kết thúc câu lệnh . } : Dấu kết thúc biểu thức điều kiện . VÍ DỤ : CONDITION { IF enable & !B & !A OUT Y0 ; IF enable & !B & A OUT Y1 ; IF enable & B & !A OUT Y2 ; IF enable & B & A OUT Y3 ; } Các tín hiệu A, B, ENABLE sau lệnh IF nếu đúng thì chọn ngõ ra là Y0...Y3, còn nếu sai thì các ngõ ra không được chọn ( xuất ).

+ FUNCTION : Từ khóa này cho phép người dùng tạo một từ khóa riêng cho mình, nó sẽ được dùng trong biểu thức logic để diễn tả một chức năng .

CÚ PHÁP : FUNCTION name ([ parameter0........parameterN]) { BODY }

Name : Là ký tự hợp lệ dùng để biểu diễn chức năng (chú ý không dùng các tên trùng với những từ khóa của CUPL) . Parameter : Một số biến đơn dùng để biểu diễn các biến khi FUNCTION được dùng trong biểu thức logic (nó không phải là một biểu thức ). Body :Là tổ hợp các biểu thức logic ,bảng sự thật ,lưu đồ trạng thái ... ( ) : Dấu dùng bao quanh các biến đơn . {} : Dấu bắt đầu và kết thúc một chức năng .

VÍ DỤ : FUNCTION xor ( in1 , in2 ) { /* in1,in2 là các thông số */ xor = in1 $ in2 ; }

Từ khóa FUNCTION sau khi được định nghĩa có thể dùng như một biểu thức. Giả sử có hai ngõ vào A và B được xem như hai thông số, Y là ngõ ra, ta có thể viết biểu thức như sau: Y = xor (A,B) ; Hoặc Y = A $ B ;

+ FIELD : Từ khóa này sau khi phát biểu ta có thể gán tên biến cho một nhóm bit trong phạm vi (32 bit) .

CÚ PHÁP : FIELD : var = [ var, var..............]; var : tên một biến hợp lệ . [var,var...] : danh sách tên biến ta liệt kê . = : toán tử gán . ; : Dấu kết thúc câu lệnh . VÍ DỤ : Tất cả các phát biểu sau tương đương nhau : FIELD : ADDRESS = [ A7,A6,A5,A4,A3,A2,A1,A0 ]; OR ADDRESS = [ A7 ....................... A0 ]; OR ADDRESS = [ A0 ....................... A7 ];

5 ví dụ sau cho biết cách sử dụng FIELD trong CULP : - ADDRESS:& = A7 & A6 & A5 & A4 & A3 & A2 & A1 & A0 ; - ADDRESS:# = A7 # A6 # A5 # A4 # A3 # A2 # A1 # A0 ; - ADDRESS:$ = A7 $ A6 $ A5 $ A4 $ A3 $ A2 $ A1 $ A0 ; - ADDRESS:hAA = A7 & !A6 & A5 & !A4 &A3 & !A2 & A1 & !A0; - ADDRESS:B01XXX11X = !A7 & A6 & A2 & A1 ; Trong 5 ví dụ trên không chú ý đến các bit. Trong ví dụ 4, giá trị của phạm vi biến được xác định bởi những giá trị logic riêng lẻ của mỗi bit, tất cả các bit được AND với nhau để tạo thành một biểu thức. Các ví dụ từ 1 đến 3 là cách dùng toán tử AND, OR, XOR cho các bit .

+ PIN : Từ khóa PIN khai báo chân vào ra của linh kiện và gán nó cho các biến tương ứng, ở đây có thể khai báo mức tác động của tín hiệu (HIGH hoặc LOW). CÚ PHÁP : PIN Pin_n = [!] var ; Pin_n : Số các chân được sử dụng [Pin_1 Pin_2......] . ! : Toán tử dùng lấy giá trị nghịch đảo của biến hiện tại . = : Toán tử gán . var : Tên các biến tương ứng với số chân khai báo . ; : Kết thúc sự khai báo . VÍ DỤ : PIN 2 = A ; /*đặt biến A vào chân số 2 tác động ở mức cao */ PIN 3 = B ; /*đặt biến B vào chân số 3 tác động ở mức cao */ + TABLE : Từ khóa này cho phép tạo một bảng sự thật theo những chức năng logic . CÚ PHÁP : TABLE var_list_1 => var_list_2 { Input_n => output_n … … input_n => output_n } ở đây : Var_list_1 : Định nghĩa các biến vào . Var_list_2 : Định nghĩa các biến ra . Input_n : Giá trị giải mã của các biến vào . Output_n : Giá trị giải mã của các biến ra . { } : Dấu đầu và cuối của biểu thức gán . => : Biểu diễn sự gán giữa biến ngõ vào và biến ngõ ra VÍ DỤ : FIELD input = [ in3......0] ; FIELD output = [out4.....0] ; TABLE input => output { 0 => 00 ; 1 => 01; 2 => 03 ; 3 => 04 ; 4 => 04; 5 => 05 ; 6 => 06 ; 7 => 07 ; 8 => 08 ; 9 => 09 ; 10 => A ; 11 => B ; 12 => C ; 13 => D ; 14 => E ; 15 => F ; } Trên đây là ví dụ đơn giản mô tả sự chuyển đổi tử số HEX sang số NHỊ PHÂN. + DEFINE : Đây là câu lệnh mà có thể thay thế một chuỗi ký tự bằng một số toán tử khác hay một số hạng .

CÚ PHÁP : $DEFINE : argument1 ,argument2 Argument1 : Tên của biến hay một ký tự đặc biệt trong mã ASCII. Argument2 : Toán tử hợp lệ ( số hay tên biến ).

Khi khai báo lệnh trên, trình biên dịch sẽ thay thế Argument1 bởi Argument2 trong suốt chương trình .

VÍ DỤ : $DEFINE ON ‘b’1 $DEFINE ON ‘b’0 $DEFINE PORT ‘h’3F0 Ngoài ra nó còn cho phép ta định nghĩa lại các toán tử logic như sau: $DEFINE / , ! $DEFINE * , & $DEFINE + , # $DEFINE :+: , $ + $IFDEF : Đây là câu lệnh đặt điều kiện dùng biên dịch từng đoạn của file nguồn . CÚ PHÁP : $IFDEF argument Argument : đối số có thể định nghĩa trước bởi lệnh $DEFINE . Khi argument được định nghĩa trước thì những lệnh theo sau &IFDEF sẽ được biên dịch cho đến khi xuất hiện một lệnh $ELSE hoặc &ENDEF . Khi argument không được định nghĩa trước thì những lệnh sau &IFDEF sẽ không được biên dịch cho đến khi xuất hiện một lệnh $ELSE hoặc &ENDEF. VÍ DỤ : &IFDEF NEVER Out1 = in1 & in2 ; Out2 = in3 # in4 ; &ENDEF Bởi vì NEVER chưa được định nghĩa nên các biều thức sẽ bị lờ đi trong suốt quá trình biên dịch . + $IFNDEF : Đây là câu lệnh đặt điều kiện dùng biên dịch từng đoạn của file nguồn .

CÚ PHÁP : IFNDEF argument Argument: Đối số có thể được định nghĩa trước hay không bởi lệnh $DEFINE. Khi argument được định nghĩa trước thì những lệnh theo sau &IFDEF sẽ không được biên dịch cho đến khi xuất hiện một lệnh $ELSE hoặc &ENDEF . Khi argument không được định nghĩa trước thì những lệnh sau &IFDEF sẽ được biên dịch cho đến khi xuất hiện một lệnh $ELSE hoặc &ENDEF. + $MACRO : CÚ PHÁP : $MACRO name argument1 argument2...argumentN macro function body $MEND Tất cả các chức năng của MACRO không được biên dịch cho đến khi tên MACRO được gọi. Giống như lệnh REPEAT, các phép toán có thể được dùng bên trong tất cả các chức năng của MACRO nhưng phải đóng trong dấu {}. VÍ DỤ : Mô tả cách sử dụng lệnh MACRO, dùng MACRO để định nghĩa chức năng giải mã của một số bit tùy ý: $MACRO decoder bits MY_X MY_Y MY_enable; FIELD select = [MY_Y{bits-1}..0] ; &REPEAT i = [ 0..{2**(bits-1)] !MY_X{i} = select:’h’{i} & MY_enable ; &REPEND $MEND decoder(3,out,in,enable) /*gọi macro */ Khi đó macro sẽ tạo những biểu thức mở rộng như sau : FIELD sel = [ in2.....0 ]; !out0 = sel:’h’0 & enable ; !out1 = sel:’h’1 & enable ; !out2 = sel:’h’2 & enable ; !out3 = sel:’h’3 & enable ; !out4 = sel:’h’4 & enable ; !out5 = sel:’h’5 & enable ; !out6 = sel:’h’6 & enable ; !out7 = sel:’h’7 & enable ;

+ MEND : dùng để kết thúc câu lệnh MACRO .

+ UNDEF : CÚ PHÁP : UNDEF argument Argument : Là đối số đã được dùng trong lệnh $DEFINE . Để giảm chuỗi ký tự hay những định nghĩa với lệnh $DEFINE ta thường dùng lệnh $UNDEF để lấy lại định nghĩa trước : $REPEAT index = [number1,number2........numberN ] repeat body $REPEND N : Có thể là một số trong dãy từ 0 -> 1023 . Trong quá xử lý thì lệnh REPEAT sẽ sao chép lại các câu lệnh từ numer 1 -> N.

VÍ DỤ : Thiết kế một mạch giải mã 3 ra 8 : FIELD sel = [in2..0 ] $REPEAT i = [0..7] !out {i} = sel:’h’{i} & enable; $REPEND Biến {i} trên đi từ 0 -> 7 với phát biểu !out{i} = ...... sẽ tạo sự lặp lại trong suốt quá trình xử lý và được tạo như sau : FIELD sel = [in2....0]; !out0 = sel:’h’0 & enable ; !out1 = sel:’h’1 & enable ; !out2 = sel:’h’2 & enable ; !out3 = sel:’h’3 & enable ; !out4 = sel:’h’4 & enable ; !out5 = sel:’h’5 & enable ; !out6 = sel:’h’6 & enable ; !out7 = sel:’h’7 & enable ;

+ $REPEND: Câu lệnh kết thúc cho một chức năng có lệnh bắt đầu là $REPEAT .

Các toán tử (comparator ) : Trong CULP dùng bốn toán tử chuẩn cho các biểu thức luận lý. Sau đây là bảng liệt kê 4 toán tử và thứ tự ưu tiên của chúng từ cao đến thấp : ! : NOT ; & : AND ; # : OR ; $ : XOR ;

VÍ DỤ : ! A : NOT-A /* lấy giá trị đảo của A*/ A&B : A AND B /*toán tử A nhân toán tử B */ A#B : A OR B /*toán tử A cộng toán tử B */

Các phần tử mở rộng (extention) : Những phần tử mở rộng có thể được thêm vào tên của biến để chỉ ra những đặc trưng mà nó liên quan đến các nút bên trong của linh kiện lập trình, chẳng hạn như FF ngõ ra ba trạng thái. Phần mở rộng do ALTMEL-CULP cung cấp sẽ được liệt kê ở bảng sau đây. Khi chạy chương trình, trình biên dịch sẽ kiểm tra phần mở rộng để xác định xem nó có phù hợp với thiết bị, có xung đột với những phần mở rộng khác đã dùng hay không . BẢNG LIỆT KÊ EXTENTION SIDE USED DISCRIPTION .AP L Preset không đồng bộ của các FF .AR L Reset không đồng bộ của các FF .CE L Ngõ vào CE đối với FF, D_CE . .CK L Tín hiệu xung CLOCKcủa FF . .CKMUX L Đa hợp tín hiệuCLOCK . .D L Ngõ vào D của FF D . .DQ L Ngõ vào D của FF –D thanh ghi . .DFE R Chọn đường hồi tiếp cho ngõ vào D .INT L Tổ hợp các đường hồi tiếp .IO L Chọn chân hồi tiếp .J L Ngõ vào J của loại FF_JK .K L Ngõ vào K của loại FF_JK .L L Ngõ vào D của bộ chốt ảo .LQ L Ngõ vào D của bộ chốt có ngõ vào ảo .LE L Tín hiệu cho phép chốt .OE L Tín hiệu cho phép xuất .R L R ngõ vào của loại FF_RS .S L S ngõ vào của loại FF_RS .SP L Tín hiệu PRESET đồng bộ cho FF .T L Ngõ vào T của FF .TFB R Chọn đường hồi tiếp cho FF _T

Mỗi phần tử mở rộng cung cấp khả năng truy xuất đến những chức năng riêng biệt của linh kiện .

VÍ DỤ : Biểu thức ngõ ra của tín hiệu cho phép xuất dùng phần mở rộng .OE (chỉ áp dụng cho linh kiện có khả năng này). Pin2 = A ; Pin3 = B ; Pin4 = C ; Pin15 = VAR NAME; VARNAME .OE = A & B ; Với những linh kiện có chân I/O cho phép xuất thì CULP tự động tạo biểu thức xuất tùy theo cách sử dụng chân. Nếu tên biến được dùng nằm bên trái của biểu thức thì chân thêm vào được xem là ngõ ra cho phép và gán cho nó giá trị bằng 1 . PIN_NAME.OE = ‘b’1; Với những chân chỉ sử dụng như một ngõ vào thì ta chỉ gán cho nó một gía trị là 0: PIN_NAME = ‘b’0; Khi dùng FF JK hay RS... một biểu thức phải viết cho cả hai tín hiệu vào J, K hay R, S, nhưng nếu trong thiết kế chỉ sử dụng một trong hai chân thì ta dùng cấu trúc sau để bỏ bớt chân còn lại : COUNT0.J = ‘b’0 ; /*ngõ vào J không được dùng */ Tất cả các chức năng điều khiển chẳng hạn như PRESET, RESET thì thường được nối chung thành một tín hiệu cho tất cả các FF bên trong linh kiện. Khi một biểu thức biểu diễn chức năng điều khiển cho một FF thì thực chất nó đã biểu diễn cho các thanh ghi .

+ Phát biểu NEXT không có điều kiện : Phát biểu này mô tả sự chuyển từ trạng thái hiện tại sang trạng thái kế tiếp mà không cần điều kiện. Cú pháp như sau: PRESENT state_n NEXT state_n ; State _n : là giá trị giải mã của các biến trạng thái, nó cũng là giá trị ngõ ra trong lưu đồ .

+ Phát biểu NEXT có điều kiện : Phát biểu này mô tả sự chuyển từ trạng thái hiện tại sang trạng thái kế tiếp nếu gặp điều kiện trong biểu thức ngõ vào. Cú pháp như sau: PRESENT state_n IF expr NEXT state_n ; ... ... IF expr NEXT state_n ; [ DEFAULT NEXT state_n;] State _n : là giá trị giải mã của các biến trạng thái, nó cũng là giá trị ngõ ra trong lưu đồ . Exprs : Những biểu thức hợp lệ . ; : Dấu kết thúc câu lệnh .

+ Phát biểu ngõ ra đồng bộ không điều kiện : Phát biểu này mô tả sự chuyển từ trạng thái hiện tại sang trạng thái kế tiếp với ngõ ra là những biểu thức liên quan đến trạng thái chuyển, biểu diễn như sau : PRESENT state_n NEXT state_n OUT [!]var................OUT [!]var ; State _n : giá trị giải mã của các biến trạng thái . var : là tên biến được khai báo trong việc khai báo chân ngõ ra, nó không phải là biến trong từ khóa SEQUENCE state _n. [!] : toán tử dùng để lấy giá trị đảo của biến .

+ Phát biểu ngõ ra đồng bộ có điều kiện : Phát biểu này mô tả sự chuyển từ trạng thái hiện tại sang trạng thái kế tiếp. Ngõ ra là các biến thanh ghi, nó sẽ chuyển trạng thái nếu gặp điều kiện trong biểu thức ngõ vào. Cú pháp như sau : PRESENT state_n IF expr NEXT state_n OUT [!]var ... OUT[!]var ; ... ... IF expr NEXT state_n OUT [!]var ... OUT[!]var ; [ DEFAULT NEXT state_n OUT[!] var ;]

+ Phát biểu ngõ ra không đồng bộ không điều kiện : Phát biểu này biểu thị cho các biến ngõ ra không phải là thanh ghi, ngõ ra liên quan đến trạng thái hiện tại, được diễn tả như sau : PRESENT state_n OUT var ... OUT var ;

+ Phát biểu ngõ ra không đồng bộ có điều kiện : Phát biểu này biểu thị cho các biến ngõ ra không phải là thanh ghi, ngõ ra liên quan đến trạng thái hiện tại, và điều kiện của biểu thức ngõ vào, được diễn tả như sau : PRESENT state_n IF expr OUT var ... OUT var ; ... ... IF expr OUT var ... OUTvar ; [DEFAULT OUT var ... OUT var ;]

CẤU TRÚC CHƯƠNG TRÌNH NGUỒN WINCUPL :

Name XXXXX ; Partno XXXXX ; Date XX/XX/XX ; Revision XX ; Designer XXXXX ; Company XXXXX ; Assembly XXXXX ; Location XXXXX ; Device XXXXX ;

/********************************************************/ /* GHI CHU: */ /* Loai linh kien cho phep: PAL XXXX hoac GAL XXXX … */ /********************************************************/

/** Khai bao cac chan ngo vao **/

Pin = ; /* */ … … Pin = ; /* */ /** Khai bao cac chan ngo ra **/ Pin = ; /* */ … … Pin = ; /* */ /** Mo ta va dinh nghia cac gia tri tuc thoi **/ …… /** Cac phuong trinh logic **/ ……

Chương trình ví dụ : Thiết kế bộ phân kênh 3 -> 8 dùng GAL16V8 :

Name PHAN KENH ; Partno CA001 ; Date 08/06/2000 ; Revision 01 ; Designer H-H ; Company KH-TN ; Assembly NONE ; Location NONE ; Device G16V8 ; /*********************************************************/ /* Loai linh kien cho phep: G16V8 */ /*********************************************************/ /** Khai bao cac chan ngo vao **/ Pin2 = X ; Pin[3,4,5] = [S2,S1,S0] ; Pin7 = !out_enable ; /* Su dung chan 7 lam chan cho phep ngo ra*/ /* tich cuc o muc thap */ /** Khai bao cac chan ngo ra **/ Pin[12..19] = [Q7..0] ; /** Mo ta va dinh nghia cac gia tri tuc thoi **/ field select = [S2..0] ; /*Dinh nghia truong select la to hop cua S2,S1,S0*/ field output = [Q7..0] ; /*Dinh nghia truong output la to hop cua Q7 …Q0*/ /** Cac phuong trinh logic **/ Q0 = SELECT:0 & X ;/* Cac ngo ra Q0 -> Q7 co gia tri tuy thuoc vao bien */ Q1 = SELECT:1 & X ; /* X va bien to hop select */ Q2 = SELECT:2 & X ;/* Gia tri cua select mac dinh hieu theo co so HEX*/ Q3 = SELECT:3 & X ; Q4 = SELECT:4 & X ; Q5 = SELECT:5 & X ; Q6 = SELECT:6 & X ; Q7 = SELECT:7 & X ;

Từ KHÓA VÀ CÚ PHÁP :

+ EQUATION : Sử dụng từ khóa này ở đầu đoạn mô tả các phương trình dạng BOOLEAN . VÍ DỤ : EQUATIONS QA = Q2 * /Q1 * /Q0 + Q3 * Q2 + Q3 * Q1 + Q3 * Q0

Chú ý: Phần mềm PALASM cho phép cả phương trình BOOLEAN và phần mô tả lưu đồ trạng thái (state_machine) cùng một lúc xuất hiện trong một tập tin thiết kế.

+ CASE : Dùng từ khóa CASE khi muốn thiết kế một chương trình làm việc ứng với từng điều kiện được thỏa của tín hiệu .

CÚ PHÁP :

........

EQUATION

...........

CASE

VÍ DỤ : .......... EQUATION .......... CASE ( DATA [7…0]) BEGIN #hOE : BEGIN ......... END #hOF : BEGIN ......... END END Ở đây #hOF biểu thị hệ thập lục tương ứng với nhóm chân điều kiện sau từ khóa CASE (8 chân tương ứng với 8 bit nhị phân, hai số thập lục ).

Nếu biểu thị giá trị #hOF theo hệ nhị phân ta phải khai báo như sau : A = #b00001111

DATA [7...0] được viết dưới dạng một vector, là một nhóm chân input hay output sắp xếp theo thứ tự từ 0....7. Ở phần mô tả chân ta phải khai báo như sau : PIN 18..11 DATA [ 7…0] Hay PIN 6,10...8 IN [4...1]

Có nghĩa là các chân 6, 10, 9, 8 sẽ tương ứng với các tín hiệu ngõ vào IN4, IN3, IN2, IN1. Việc khai báo này cho phép ta dễ dàng so sánh hay gán một giá trị biết trước thay vì khai báo riêng lẻ từng chân .

+ IF_THEN_ESE : Cấu trúc này dùng cho các biểu thức có điều kiện và được sử dụng trong suốt quá trình mô phỏng .

CÚ PHÁP : IF (condition) THEN BEGIN Task1 END ELSE BEGIN Task2 END

Cú pháp này được sử dụng trong các quá trình thiết kế có biểu thức BOOLEAN và máy trạng thái (state machine).

VÍ DỤ : SIMULATION SETF /OE /CLOCK COUNT IF (J=5) THEN BEGIN CHECK Q0 END ELSE BEGIN CHECK /Q0 END

Ở đây chân OE ( output enable),chân CLOCK đều cố định trên linh kiện nó được quy định bởi nhà sản xuất. Chân COUNT và chân J là các chân ngõ vào do người thiết kế tùy ý chọn, trong số các chân ngõ vào .Q0 là một ngõ ra được chọn trong số các chân ra.

+ state : Từ khóa STATE dùng để mở đầu một đoạn trạng thái của tập tin thiết kế .

CÚ PHÁP : STATE <> <> <> <> <> <>

VÍ DỤ : STATE : ; state setup and defaults MOORE_MACHINE START_UP := POWER _ UP -> S3 S1 := COND1 -> S3 + COND2 -> S7 ;state ouput equations S1. OUTF := OUT1 * / OUT2 ......... ......... ; state assignment Equation S1 := /ST1 * /ST2 ........... .......... ; state condition Equation CONDITIONS CONITION1 = IN1 * /IN2 * IN3 ............. ..............

Từ khóa STATE mở đầu đoạn trạng thái, sau từ khóa này ta có thể dùng từ khóa để mặc định các trạng thái như sau :

Thiết đặt và mặc định trạng thái(State Setup and Defaults ):

Dùng từ khóa MOORE_MACHINE hoặc MEALY_MACHINE để phân loại các máy trạng thái (state machine) mà ta đang thiết kế . Trạng thái MOORE : Các tín hiệu hiện diện trên các ngõ ra hệ thống trong một trạng thái chỉ được xác định bởi các biểu thức logic giải mã và các mức logic hiện diện ở ngõ ra của các Flip-Flop, chứ không bởi bất cứ tín hiệu ngoài nào (tín hiệu ngoài là các tín hiệu tác động từ bên ngoài vào linh kiện hay tín hiệu từ lối vào). Vì thế những thay đổi trong các tín hiệu ngoài chỉ có thể ảnh hưởng đến các tín hiệu ra của hệ thống sau khi có xung nhịp ( CLOCK ) kế tiếp xảy ra . Trạng thái MEALY : Các tín hiệu trên các ngõ ra hệ thống được xác định bằng các mức logic trên ngõ ra của Flip-Flop và bởi bất cứ tín hiệu ngoài nào được nối vào các ngõ vào của hệ giải mã ngõ ra. Vì thế bất cứ tín hiệu ngoài nào tác động đến ngõ vào đều ảnh hưởng trực tiếp đến các tín hiệu ra của hệ thống .

+ START_UP : Từ khóa này cho chúng ta “khởi động” (POWER UP ) một trạng thái đặc trưng hoặc phân nhánh một cách không đồng bộ đến trạng thái mới mỗi khi một điều kiện khởi tạo xuất hiện .

CÚ PHÁP : START_UP := POWER_UP -> state1

+ CONDITION -> state2

Trong đó POWER_UP : là một từ khóa dùng để bắt đầu chuyển tiếp từ trạng thái được chỉ định trong sơ đồ thiết kế trạng thái máy (có sử dụng các F_F để chuyển trạng thái ). Nếu không có từ khóa này thì trình biên dịch PALASM sẽ mặc định sự chuyển tiếp bắt đầu từ trạng thái đầu tiên được mô tả trong đoạn "các phương trình chuyển tiếp trạng thái" (state transition equations) sang trạng thái tiếp theo .

Trong ví dụ trên nếu không có khai báo dòng : START_UP := POWER_UP -> state3

thì khi đó chương trình sẽ mặc định chuyển tiếp trạng thái bắt đầu từ trạng thái S1.

+ Các phương trình trạng thái : Các phương trình này có nhiệm vụ hướng dẫn cho thiết bị chuyển đến trạng thái được chỉ định nó tùy thuộc vào giá trị của tín hiệu điều kiện .

Khai báo các phương trình như sau :

<> := <> -> <>

+ <> ->

Ở ví dụ này, nếu COND1 = 1 thì trạng thái sau S1 sẽ là trạng thái S3, nếu COND2 := 1 thì trạng thái chuyển đến kế tiếp là S7. Trạng thái S2 do sử dụng điều kiện là Vcc, tức là mặc định điều kiện luôn luôn đúng (Vcc = 1), nên trạng thái kế tiếp sẽ luôn luôn là S3. Trạng thái S3 nếu thỏa điều kiện COND3 := 1 thì chuyển đến trạng thái kế tiếp là S4, còn COND3 := 0 thì chuyển đến trạng thái là S2. Ta dùng ký hiệu + -> để biểu diễn trạng thái mặc định nội bộ “local default” sẽ chuyển đến, nếu các điều kiện trước không thỏa .

+ Phương trình trạng thái ngõ ra : Dùng các phương trình này để điều khiển ngõ ra của máy trạng thái.

Khai báo các phương trình như sau : Statename .OUT =

VÍ DỤ : ......... S1. OUT = OUT1 * /OUT2

Trong ví dụ này khi chuyển đến trạng thái S1 thì các ngõ ra của trạng thái S1 sẽ có giá trị tương ứng như giá trị chân OUT1, OUT2, ở đây giá trị tương ứng là 1 và 0 .

+ Phương trình trạng thái điều kiện : Dùng để định nghĩa các điều kiện khi chuyển trạng thái .

Đoạn mô phỏng : SIMULATION TRACE_ON <> ............. TRACE_OFF

Đoạn mô phỏng này nhằm kiểm tra lại quá trình chuyển trạng thái của máy trạng thái. Kết quả mô phỏng sẽ được trình biên dịch ghi lại ở file có đuôi là *.SIM. Việc mô phỏng không làm ảnh hưởng đến file nạp vào thiết bị ( file có đuôi *.JED), đoạn mô phỏng có chức năng tương tự như đoạn mô phỏng của chương trình biên dịch ABEL hoặc WIN_CUPL (bắt đầu bằng từ khóa TEST_VECTOR). VÍ DỤ : giải mã 2 -> 4 : …… SIMULATION TRACE_ON IN1 IN2 OUT1 OUT2 OUT3 OUT4 SETF /OE SETF /IN1 /IN2 CLOCKF CLK CHECK /OUT1 OUT2 OUT3 OUT4 SETF /IN1 IN2 CLOCKF CLK CHECK OUT1 /OUT2 OUT3 OUT4 SETF IN1 /IN2 CLOCKF CLK CHECK OUT1 OUT2 /OUT3 OUT4 SETF IN1 IN2 CLOCKF CLK CHECK OUT1 OUT2 OUT3 /OUT4 TRACE_OFF

Từ khóa SIMULATION đặt ở đầu đoạn mô phỏng.

Từ khóa TRACE_ON cho biết bắt đầu quá trình mô phỏng, sau từ khóa TRACE_ON là tên các trạng thái, chân ngõ vào, ngõ ra tham gia quá trình mô phỏng, từ khóa TRACE_OFF kết thúc quá trình mô phỏng.

Từ khóa SETF nhằm để gán giá trị cho các chân ngõ vào hoặc các nút cần mô phỏng. SETF /OE : mô phòng chân OE xuống mức thấp.

Từ khóa CLOCKF mô phỏng 1 xung clock đưa vào ngõ vào CLK.

Từ khóa CHECK dùng để kiểm tra 1 hoặc một nhóm các tín hiệu ngõ ra khi mô phỏng. Thông thường sử dụng lệnh CHECK để kiểm tra ngõ ra từng bước của quá trình mô phỏng, kết hợp với việc giả lập 1 hay 1 nhóm ngõ vào thay đổi giá trị logic. Các giá trị sau từ khóa CHECK là các giá trị ngõ ra được dự đoán.

* CHƯƠNG TRÌNH VÍ DỤ : Chương trình giải mã 3 sang 8 đường :

;PALASM Design Description ;---------------------------------- Declaration Segment ------------ TITLE TUTOR1.PDS PATTERN A REVISION 1.0 AUTHOR J.ENGINEER COMPANY ADVANCED MICRO DEVICES DATE 01/01/90

CHIP DECODER PAL16L8

;---------------------------------- PIN Declarations --------------- PIN 2 X COMBINATORIAL ; INPUT PIN 3 Y COMBINATORIAL ; INPUT PIN 4 Z COMBINATORIAL ; INPUT PIN 10 GND ; INPUT PIN 12 A COMBINATORIAL ; OUTPUT PIN 13 B COMBINATORIAL ; OUTPUT PIN 14 C COMBINATORIAL ; OUTPUT PIN 15 D COMBINATORIAL ; OUTPUT PIN 16 E COMBINATORIAL ; OUTPUT PIN 17 F COMBINATORIAL ; OUTPUT PIN 18 G COMBINATORIAL ; OUTPUT PIN 19 H COMBINATORIAL ; OUTPUT PIN 20 VCC ; INPUT

;----------------------------------- Boolean Equation Segment ------ EQUATIONS /A = /X * /Y * /Z /B = /X * /Y * Z /C = /X * Y * /Z /D = /X * Y * Z /E = X * /Y * /Z /F = X * /Y * Z /G = X * Y * /Z /H = X * Y * Z

;----------------------------------- Simulation Segment ------------ SIMULATION TRACE_ON X Y Z A B C D E F G H SETF /X /Y /Z CHECK /A B C D E F G H SETF /X /Y Z CHECK A /B C D E F G H SETF /X Y /Z CHECK A B /C D E F G H SETF /X Y Z CHECK A B C /D E F G H SETF X /Y /Z CHECK A B C D /E F G H SETF X /Y Z CHECK A B C D E /F G H SETF X Y /Z CHECK A B C D E F /G H SETF X Y Z CHECK A B C D E F G /H TRACE_OFF

Không có nhận xét nào:

Đăng nhận xét